# Parallel and Vectorized Wavelet Tree Construction

Master's Thesis of

Marcel Hollerbach

at the Department of Informatics Theoretical Informatics Karlsruhe Institude of Technology

Reviewer: Prof. Dr. Peter Sanders

Advisor: Dr. Florian Kurpicz

01. September 2021 – 01. March 2022

Karlsruher Institut für Technologie Fakultät für Informatik Postfach 6980 76128 Karlsruhe

| I declare that I have developed and written the enclosed thesis completely by myself, and have not used sources or means without declaration in the text.  PLACE, DATE |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Throu, Ditt                                                                                                                                                            |

| (Marcel Hollerbach)                                                                                                                                                    |

## **Abstract**

The wavelet tree [13] is a fast look up structure for strings over an alphabet  $[0, \sigma)$  and the length n. It can be used to answer rank, select, and access queries in  $O(\log \sigma)$  time. In this work, the algorithms of Kaneta [9] are implemented. This implementation is based on the work of Babenko et al. [10] and Munro et al. [4], they showed that wavelet trees could be build in  $O\left(n\log(\sigma)/\sqrt{\log(n)}\right)$  by utilizing table look ups to process entire words. Kaneta implemented this approach using special instruction like *pext*, and *pshufl*, which replaced the need of creating tables. Additionally, parallel versions are implemented by using domain decomposition. As an additional parallel construction, the approach of [8] is implemented. As before, the table look ups are replaced with *pext* instructions. All the construction algorithms implemented are then compared to PWM from Dinklage et al. [2], which require  $O(n \log(\sigma))$  time for construction. In the comparison of PWM with the sequential algorithms, the pext tree creation were able to outperform the PWM algorithms for  $\log \sigma > 3$ . For matrix creation, they only performed better for  $\log \sigma > 5$ . Comparing the parallel approaches of domain decomposition and the approach of Shun showed, that domain decomposition performs a lot better compare to Shun. Comparing the domain decomposition of PWM with the one of the *pext* algorithms showed that the pext versions are outperforming the PWM versions. This time only for  $\log \sigma = 8$  for the biggest payloads. And  $\log \sigma > 6$  for medium sized payloads. Additionally to that, the relation between  $\tau$  and log  $\sigma$  is getting explained. Finally, a new alternative approach to the algorithm from Babenko et al. and Munro et al. is described.

## Zusammenfassung

Wavelet trees [13] werden als Index für Zeichenketten über ein  $[0, \sigma)$  und einer Länge n genutzt. Der Index wird genutzt um rank, select und access Anfragen zu beantworten. Diese Anfragen beantworten wie oft ein Buchstabe vorkommt, wo der n-te Buchstabe in der Zeichenkette vorkommt, oder welcher Buchstabe an einer bestimmten Position steht. All diese Anfragen können in  $O(\log \sigma)$  Zeit beantwortet werden. In den Arbeiten von Babenko et al. [10] und Munro et al. [4] wurde erstmals ein ansatz gezeigt, indem man Wavelet Strukturen in  $O\left(n\log(\sigma)/\sqrt{\log(n)}\right)$  Zeit Konstruieren kann. Dieser Ansatz nutzt dabei Tabellen, um mehrere Bits auf einmal zu verarbeiten. In der Arbeit von Kaneta [9] werden diese Tabellen dann durch Instruktionen wie pext und pshufl ersetzt. Das resultiert darin, dass die theoretisch benötigte Zeit von  $O(n\log(\sigma))$  auf  $O\left(n\log(\sigma)/\sqrt{\log(n)}\right)$ verringert wird. In dieser Arbeit werden diese Algorithmen mit pext zunächst erneut implementiert. Dann werden diese durch Domain Decomposition parallelisiert. Zusätzlich wird ein weiterer Ansatz von Shun [8] implementiert. Dieser bildet eine Alternative zur Domain Decomposition. Im zweiten Teil der Arbeit werden dann die sequentiellen Algorithmen von Dinklage et al. [2] mit den pext Versionen verglichen. Dabei zeigt sich, das die pext Algorithmen für  $\log \sigma > 3$  schneller als diese in PWM sind. Die Matrix zu erstellen ist ebenfalls schneller für  $\log \sigma > 5$ . Der Vergleich der beiden parallelen Versionen von Domain Decomposition und dem Ansatz von Shun zeigt, dass die Domain Decomposition wesentlich schneller ist, als die von Shun. Die Domain Decomposition wird dann mit den parallelen Algorithmen von PWM verglichen. Dabei zeigt sich, dass hier die pext Versionen bei großen Eingaben für  $\log \sigma > 8$  schneller als die PWM Algorithmen sind. Bei mittleren Eingabegrößen sogar für  $\log \sigma > 6$ . Zusätzlich wird in der Arbeit der Zusammenhang zwischen  $\tau$  und log  $\sigma$  erklärt. Letztlich wird noch ein neuer Ansatz vorgestellt, welcher die Idee von Babenko et al. und Munro et al. aufgreift, und diese leicht verändert.

## **Contents**

| Ab | Abstract |                                                              |  |  |  |  |  |  |  |  |  |  |

|----|----------|--------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|

| Zu | samn     | nenfassung                                                   |  |  |  |  |  |  |  |  |  |  |

| 1. | Intro    | oduction                                                     |  |  |  |  |  |  |  |  |  |  |

|    | 1.1.     | Related Work                                                 |  |  |  |  |  |  |  |  |  |  |

|    | 1.2.     | Wavelet Tree and Wavelet Matrix                              |  |  |  |  |  |  |  |  |  |  |

|    |          | 1.2.1. Rank / Select Queries on Wavelet Trees and Matrices   |  |  |  |  |  |  |  |  |  |  |

|    | 1.3.     | Additional Instructions                                      |  |  |  |  |  |  |  |  |  |  |

|    | 1.4.     | Algorithem Parallelization                                   |  |  |  |  |  |  |  |  |  |  |

|    | 1.5.     | Contribution                                                 |  |  |  |  |  |  |  |  |  |  |

| 2. | Sequ     | uential Algorithms                                           |  |  |  |  |  |  |  |  |  |  |

|    | 2.1.     | Bignode Tree Building                                        |  |  |  |  |  |  |  |  |  |  |

|    | 2.2.     | Creating Wavelet Tree and Wavelet Matrix out of Bignode Tree |  |  |  |  |  |  |  |  |  |  |

|    |          | 2.2.1. Wavelet Tree Construction                             |  |  |  |  |  |  |  |  |  |  |

|    |          | 2.2.2. Wavelet Matrix Construction                           |  |  |  |  |  |  |  |  |  |  |

|    |          | 2.2.3. Influence of $\tau$                                   |  |  |  |  |  |  |  |  |  |  |

|    |          | 2.2.4. Runtime                                               |  |  |  |  |  |  |  |  |  |  |

|    | 2.3.     | Dynamic $\tau$ Adjustment                                    |  |  |  |  |  |  |  |  |  |  |

| 3. | Para     | llel Algorithms                                              |  |  |  |  |  |  |  |  |  |  |

|    | 3.1.     | Domain Decomposition                                         |  |  |  |  |  |  |  |  |  |  |

|    | 3.2.     | Shun Parallelization                                         |  |  |  |  |  |  |  |  |  |  |

| 4. | Eval     | uation                                                       |  |  |  |  |  |  |  |  |  |  |

|    | 4.1.     | Sequential Runtime of Basic Settings                         |  |  |  |  |  |  |  |  |  |  |

|    | 4.2.     | Comparing Domain Decomposition Mergers                       |  |  |  |  |  |  |  |  |  |  |

|    | 4.3.     | Comparing Shun and Domain Decomposition                      |  |  |  |  |  |  |  |  |  |  |

|    | 4.4.     | Comparing to PWM                                             |  |  |  |  |  |  |  |  |  |  |

|    |          | 4.4.1. Comparing using Real World Data                       |  |  |  |  |  |  |  |  |  |  |

|    |          | 4.4.2. Comparing using Generated Data                        |  |  |  |  |  |  |  |  |  |  |

|    | 4.5.     | Memory Consumption                                           |  |  |  |  |  |  |  |  |  |  |

|    | 4.6.     | Intrinsic Functions                                          |  |  |  |  |  |  |  |  |  |  |

|    | 4.7.     | Code-Size                                                    |  |  |  |  |  |  |  |  |  |  |

|    | 4.8.     | Runtime prediction for dynamic $\tau$ setting                |  |  |  |  |  |  |  |  |  |  |

| 5. | Con      | clusion                                                      |  |  |  |  |  |  |  |  |  |  |

|    | 5.1.     | Conclusion over <i>pext</i> algorithms                       |  |  |  |  |  |  |  |  |  |  |

#### Contents

|     | 5.2.     | Further Improvements                               | 50 |  |  |  |  |  |  |  |  |  |

|-----|----------|----------------------------------------------------|----|--|--|--|--|--|--|--|--|--|

| Bil | oliogra  | aphy                                               | 51 |  |  |  |  |  |  |  |  |  |

| A.  | Appendix |                                                    |    |  |  |  |  |  |  |  |  |  |

|     | A.1.     | Parallel wavelet construction using generated data | 54 |  |  |  |  |  |  |  |  |  |

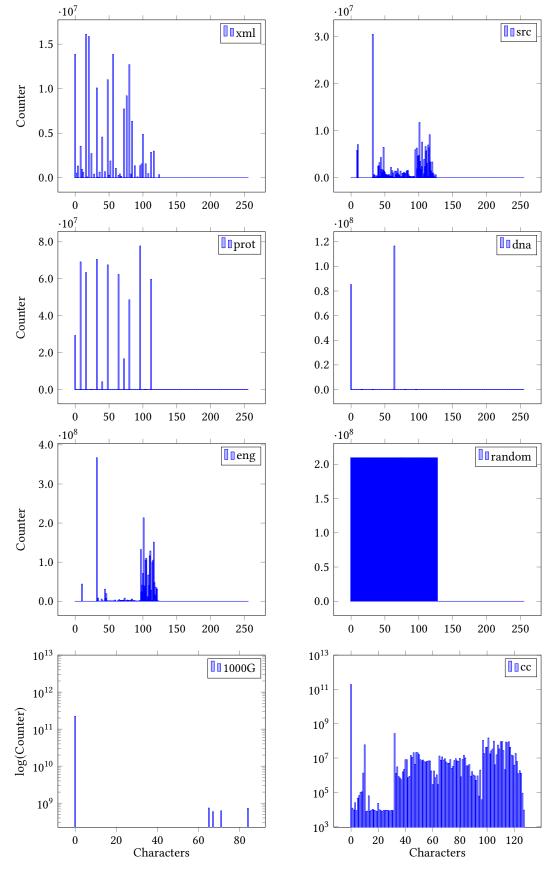

|     | A.2.     | Histograms of example texts                        | 57 |  |  |  |  |  |  |  |  |  |

## **List of Figures**

| 1.1.                                | Visualization of a wavelet tree for $\log \sigma = 4$ . Each cell has always 2 children, and characters initially in the cell, must end up in one of its                                                                                                                                                   |    |

|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.0                                 | children. Additionally, the length of all cells of a level is always $n$                                                                                                                                                                                                                                   | 3  |

| 1.2.                                | Visualization of a wavelet matrix for $\sigma = 4$ . Each cell has always 2 children, and characters initially in the cell, must end up in one of its children. The                                                                                                                                        |    |

|                                     | big difference to the tree is here, that the order of children cells is different.                                                                                                                                                                                                                         | 3  |

| 1.3.                                | The wavelet tree of the word <i>hello world</i> . The vertical lines are showing                                                                                                                                                                                                                           |    |

|                                     | where each cell starts or ends. Not each line fills all available cells, hence                                                                                                                                                                                                                             |    |

|                                     | the number of visible cells is not always the maximum that is possible                                                                                                                                                                                                                                     | 4  |

| 1.4.                                | The wavelet matrix of the word <i>hello world</i> . The vertical lines are separating                                                                                                                                                                                                                      |    |

|                                     | the 0s cells from the 1s cells. If one cell is empty, no vertical line is added.                                                                                                                                                                                                                           | 1  |

| 1.5.                                | Explanation of the <i>pext</i> semantics. A/B/C/D/E/F/G/H are placeholders for                                                                                                                                                                                                                             | 4  |

| 1.5.                                | bits                                                                                                                                                                                                                                                                                                       | 5  |

| 2.1.                                | Overview showing the relation between input, first phase, second phase, bignode tree, and resulting wavelet tree. The arrows of the first phase display that these values are represented in the associated line. The arrows of the second phase show in which lines the <i>pack</i> operation results are |    |

|                                     | stored.                                                                                                                                                                                                                                                                                                    | 9  |

| <ul><li>2.2.</li><li>2.3.</li></ul> | Example bignode tree for in the input sequence <i>hello world</i> and $\tau = 2$ Constant values $\ell$ and $h$ for $\tau = 4$ , which are used for <i>split&amp;sort</i> and <i>pack</i>                                                                                                                  | 11 |

|                                     | operations.                                                                                                                                                                                                                                                                                                | 12 |

| 2.4.                                | Subtraction result of a block                                                                                                                                                                                                                                                                              | 13 |

| 2.5.                                | with a MSB not being set                                                                                                                                                                                                                                                                                   | 13 |

| 2.3.                                | with a MSB being set                                                                                                                                                                                                                                                                                       | 13 |

| 2.6.                                | Results of the <i>splitsort</i> (0, <i>input</i> ) call. $L_0$ contains all blocks that have a 0 at                                                                                                                                                                                                        |    |

|                                     | block position 0. $L_1$ contains all blocks that have a 1 at block position 1.                                                                                                                                                                                                                             |    |

|                                     | Each result has two blocks of result                                                                                                                                                                                                                                                                       | 14 |

| 2.7.                                | Results of a <i>pack(1, input)</i> call                                                                                                                                                                                                                                                                    | 14 |

| 2.8.                                | An example histogram line, and bignode line at $i = 2$ . The bignode tree                                                                                                                                                                                                                                  |    |

|                                     | line is stored using $\beta = 8$ . There are 4 cells in total, which are stored in 2                                                                                                                                                                                                                       |    |

| 0.0                                 | 8-bit long words                                                                                                                                                                                                                                                                                           | 15 |

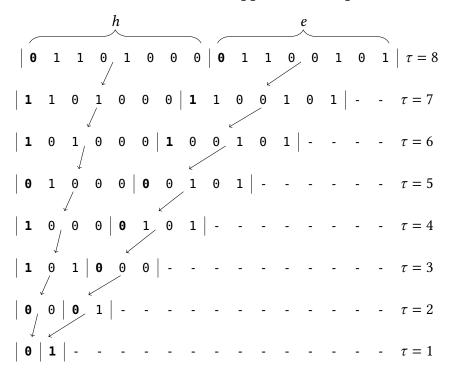

| 2.9.                                | Wavelet tree construction for the input 'he'. Each new line is after a                                                                                                                                                                                                                                     |    |

|                                     | split&sort and pack call. Each pack call is extracting the bold numbers.  The split&sort call is sorting based on the bold character                                                                                                                                                                       | 20 |

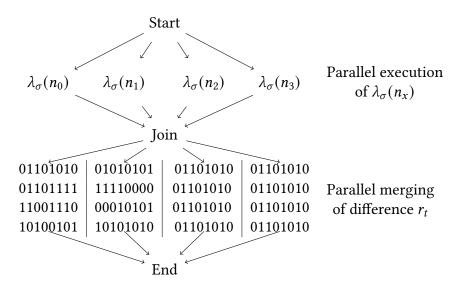

| <ul><li>3.1.</li><li>3.2.</li></ul> | Diagram showing the threaded parts of domain decomposition. The example input has 32 characters, the calculation unit has 4 parallel units. $n_x$ with $x \in 0, 1, 2, 3$ , the $x$ 'th part of the input is meant. The picture shows, that the execution of $\lambda_{\sigma}$ as well as the merging is parallelized                                                                                                                                                                      | 22       |

|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

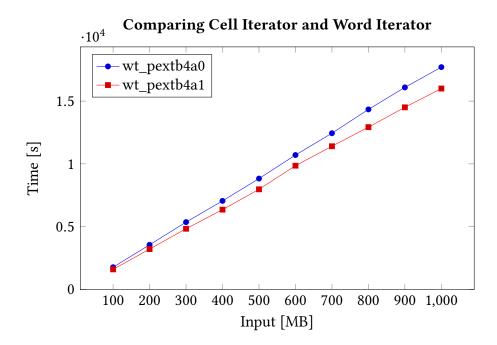

| 4.1.                                | Comparison of tree construction for cell iterator and word iterator with a                                                                                                                                                                                                                                                                                                                                                                                                                  | 91       |

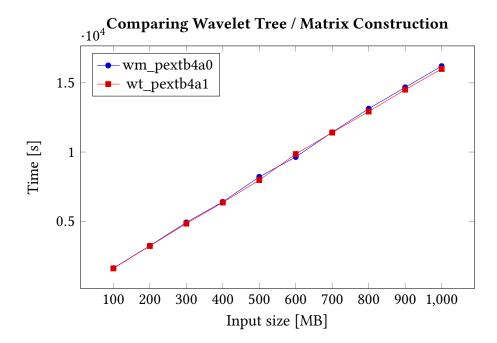

| 4.2.                                | $\tau$ of 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 31       |

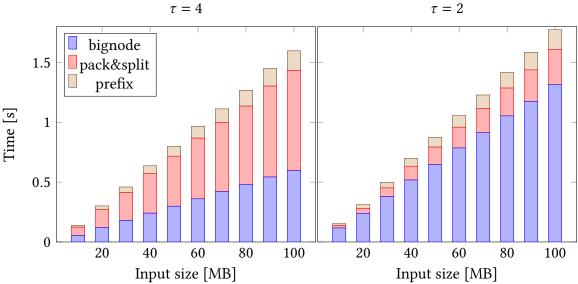

| 4.3.                                | The two plots show the internals of wavelet matrix construction, for $\log \sigma = 8$ . On the left side for $\tau = 4$ on the right side $\tau = 2$ . The prefix phase is the one creating the histogram, the bignode phase is building the bignode tree. And the pack&split phase transforms the bignode tree into the result object. Finally, this shows that the bignode building takes longer when there is a smaller $\tau$ . As input, randomized content with $\log \sigma = 8$ is |          |

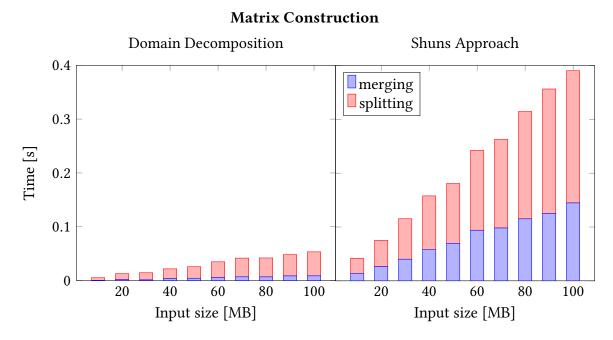

| 4.4.                                | used                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 33       |

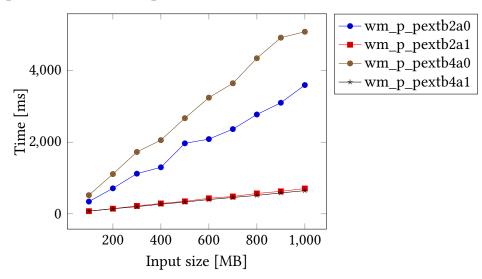

| 4.5.                                | with $\log \sigma = 8$ is used                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 34       |

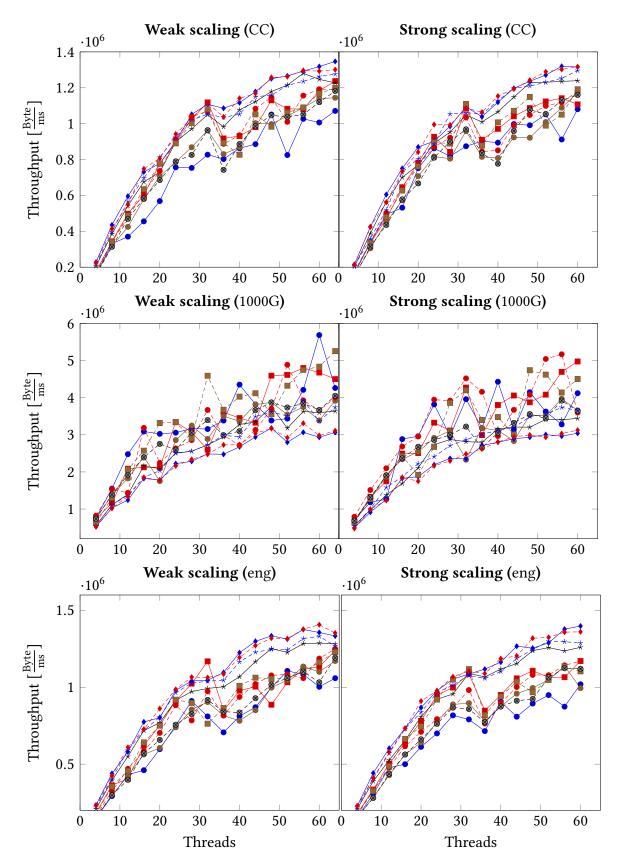

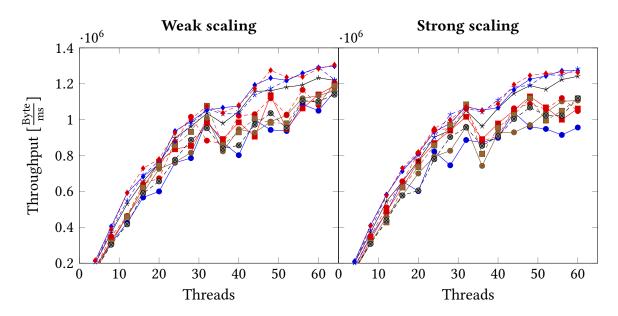

| 4.6.                                | to Shuns approach. The construction runs with $\tau = 4$ and 64 threads Weak and strong scaling experiments for the real world data. In weak                                                                                                                                                                                                                                                                                                                                                | 35       |

| 4.7.                                | scaling, 100M per thread are added. In strong scaling 6400MB are performed. Weak scaling experiment, per thread 100MB are assigned. In each step 4 more threads are added                                                                                                                                                                                                                                                                                                                   | 39<br>44 |

| 4.8.                                | Strong scaling experiment with 6,4GB of payload. With each step 4 more threads are added.                                                                                                                                                                                                                                                                                                                                                                                                   | 17       |

| 4.9.                                | Plot of memory usage divided by the payload size. The plot shows 6 cluster. Two clusters are from the PWM algorithm. Two from the normal <i>pext</i> algorithm and their domain decomposition versions. The last 2 clusters are from the Shun parallelization. For parallel constructions, 64 threads are used                                                                                                                                                                              | 44       |

| 4.10.                               | Plots showing the difference between the internal phases of the construc-                                                                                                                                                                                                                                                                                                                                                                                                                   | 45       |

## **List of Tables**

| 4.1.  | All algorithms described in this work. All for $\tau \in 2, 4, \ldots$                                         | 29  |

|-------|----------------------------------------------------------------------------------------------------------------|-----|

| 4.2.  | Construction time with different block sizes $	au$ in bits. Each algorithm name                                |     |

|       | written as $wm_{\log \sigma}$ . All evaluated with payload of the size 1000M. All times                        |     |

|       | in s. $\tau > \log \sigma$ are not evaluated. The algorithm $wt0$ is the word iterator,                        |     |

|       | wt1 is the cell iterator                                                                                       | 30  |

| 4.3.  | Runtime construction methods, parallelized using domain decomposition,                                         |     |

|       | for wavelet structures. The first two columns are for matrix construction,                                     |     |

|       | the left construction times for the merger described here, on the right those                                  |     |

|       | of the PWM repository. The second two columns are for tree construction.                                       |     |

|       | The right one for the matrix construction. As input, randomized content                                        |     |

|       | with $\log \sigma = 8$ is used. The columns called <i>Thesis Merger</i> is referring to the                    |     |

|       | merger explained in 3.1. The columns called <i>PWM Merger</i> are referring to                                 |     |

|       | the merger of Dinklage et al. [2]. All values in ms                                                            | 33  |

| 1 1   |                                                                                                                | 33  |

| 4.4.  | These payloads are transformed into an alphabet without unused charac-                                         |     |

|       | ters. This results in a more compact alphabet, where the $\log \sigma$ value has a                             |     |

|       | direct impact on the depth of the levels that need to be walked. The script                                    |     |

|       | for transforming the input can be found in the repository of this work.                                        |     |

|       | From payload <i>CC</i> and <i>1000G</i> , only a 80GB prefix is used, as the original                          | 0.6 |

|       | payload was too big for the available hardware.                                                                | 36  |

| 4.5.  | Comparison of constructing wavelet tree times for real datasets. The <i>pext</i>                               |     |

|       | algorithm is the cell iterator approach. Each result in <i>ms.</i>                                             | 37  |

| 4.6.  | Comparison of constructing wavelet matrix times for real datasets. Each                                        |     |

|       | result in <i>ms</i>                                                                                            | 37  |

| 4.7.  | Comparing construction times for parallel tree creation. Each result in <i>ms</i> .                            | 38  |

| 4.8.  | Comparing construction times for parallel matrix creation. Each result in <i>ms</i> .                          | 38  |

| 4.9.  | Sequential speedups of wavelet tree creation and the fastest PWM algo-                                         |     |

|       | rithm, with payloads with different $\log \sigma$ . Each column is described as                                |     |

|       | $s_{\lceil \log \sigma \rceil}$ . With 64 threads                                                              | 41  |

| 4.10. | Sequential speedups of wavelet matrix creation and the fastest PWM                                             |     |

|       | algorithm, with payloads with different $\log \sigma$ . Each column is described as                            |     |

|       | $s_{\lceil \log \sigma \rceil}$ . With 64 threads                                                              | 41  |

| 4.11. | Parallel speedups for wavelet tree creation with payloads with different                                       |     |

|       | $\log \sigma$ . Each column is described as $s_{\lceil \log \sigma \rceil}$ . With 64 threads. Further details |     |

|       | can be received from A.1                                                                                       | 42  |

| 4.12. | Parallel speedups for wavelet matrix creation with payloads with different                                     |     |

|       | $\log \sigma$ . Each column is described as $s_{\lceil \log \sigma \rceil}$ . With 64 threads. Further details |     |

|       | can be received from A.1                                                                                       | 43  |

| 4.13. | Different code sizes compared in lines. For <i>pext</i> , cell iteration for tree      |    |

|-------|----------------------------------------------------------------------------------------|----|

|       | building is evaluated. The phase <i>flushing</i> is constructing the result buffer.    |    |

|       | For PWM algorithm this is the normal insertion of bits according to <i>pc</i> ,        |    |

|       | ps, or pc_ss. For pext, Shuns algorithms this is the transformation from               |    |

|       | bignode tree to result                                                                 | 46 |

| 4.14. | Table showing the prognoses for the alternative algorithm approach de-                 |    |

|       | scribed. The prognoses are calculated using Formula 4.1. The input values              |    |

|       | $t_8$ , $t_4$ , and $t_2$ are used from measuring the internals of the algorithms with |    |

|       | $\tau = 8$ $\tau = 4$ and $\tau = 2$ All values in seconds                             | 47 |

## 1. Introduction

The wavelet structure [13] is a space efficient lookup structure. The work of Dinklage et al. [2] also gives a survey, that gives further use cases in compression, computational geometry, and a helper to create the Burrows-Wheeler Transform. Further information can be found in the Introduction of Dinklage et al. It can be used to answer rank / select queries. The wavelet structure itself, is build from an input string. Each character of the input string is within the range  $[0, \sigma)$ . Therefore each character requires at least  $\lceil \log \sigma \rceil$  bits to be stored. In practice, a single character is always stored in a multiple of 8-bit long character.

In the next Section 1.1, a brief overview of the current states is given, after that, the wavelet tree and matrix are explained in Section 1.2. Then, intrinistic functions, which will get used in this work are explained in Section 1.3. After that, basics for parallel algorithms are introduced 1.4. In the next Chapters 2 and 3 these basic blocks are used to introduce the algorithms.

#### 1.1. Related Work

In this work a range of different algorithms are implemented. All of them do use assembler instructions used by Keneta in [9]. Additionally, those algorithms are compared to those from the work of Johannes Dinklage et al. [2]. They introduced a github <sup>1</sup> repository, this repository is collecting a wide range of algorithms. The algorithms pc, ps, pc\_ss and the domain decomposition of those are used for comparison, as they are the fasted sequential construction algorithms, as well as the fasted parallel constructions. The algorithms are briefly explained in Section 4.4. The algorithms in PWM do construction in  $O(n\log(\sigma))$ . Munro et al. [4] and Babenko et al. [10] showed that construction is also possible in  $O\left(n\log(\sigma)/\sqrt{\log(n)}\right)$  time, however, this was only shown theoretically. In 2018, Kaneta implemented those theoretical ideas in [9]. He used so called *pext* instructions to use RAM bit-wise parallism for the construction algorithms. He also implemented versions using *pshufl* instructions. However, the *pext* versions showed to be the fastest for tree constructions. For matrix construction *pext* and *pshufl* instructions both have been fast. However, in this work only *pext* versions have been used.

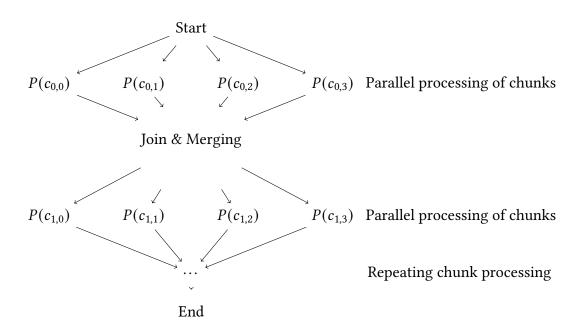

For parallel construction there are multiple construction algorithms in PWM [2]. A few do use customized parallelization strategies. Other versions in PWM do use domain decomposition. The fastest parallel algorithms are those utilizing domain decomposition. This also applies to other works from Fuentes-Sepúlveda et al. [5], and Labeit et al. [7]. Additionally to that, Shun [8] is proposing an alternative parallel algorithm that is not

<sup>&</sup>lt;sup>1</sup>Github repository hosted at: https://github.com/kurpicz/pwm

using domain decomposition. This work also uses the ideas of Munro et al. [4] and Babenko et al. [10]. Shun proposes to use parallel integer sorting, described in [12] and [14], to run the first phase. The second phase is then parallelized individually.

#### 1.2. Wavelet Tree and Wavelet Matrix

The wavelet tree and matrix structure is a perfectly balanced binary tree like object, with bit vectors in its nodes. For a given input sequence of length n, with a alphabet size of  $\sigma$ , the tree has  $\lceil \log \sigma \rceil$  levels. Every edge between a child node and its parent has a associated 0 or 1. This association is later used to explain the construction, however, it is not stored. The exact meaning of these labels depends on if this is a wavelet tree or matrix. Every node it this wavelet structure has a level, the level is the number of edges between the node, and root, these levels are annotated as  $i \in [0, \lceil \log \sigma \rceil)$ . Each node in a level has an index x. In a level i there are  $2^i$  different nodes. In the following two paragraphs, the relation between children and theire parent nodes are explained. The example memory representation in the next sections are representing the character sequence *hello world*. The bit representation of these characters are:

| char | Bit representation |   |   |   |   |   |   |   |  |  |  |  |

|------|--------------------|---|---|---|---|---|---|---|--|--|--|--|

| h    | 0                  | 1 | 1 | 0 | 1 | 0 | 0 | 0 |  |  |  |  |

| e    | 0                  | 1 | 1 | 0 | 0 | 1 | 0 | 1 |  |  |  |  |

| 1    | 0                  | 1 | 1 | 0 | 1 | 1 | 0 | 0 |  |  |  |  |

| 1    | 0                  | 1 | 1 | 0 | 1 | 1 | 0 | 0 |  |  |  |  |

| o    | 0                  | 1 | 1 | 0 | 1 | 1 | 1 | 1 |  |  |  |  |

|      | 0                  | 0 | 1 | 0 | 0 | 0 | 0 | 0 |  |  |  |  |

| w    | 0                  | 1 | 1 | 1 | 0 | 1 | 1 | 1 |  |  |  |  |

| O    | 0                  | 1 | 1 | 0 | 1 | 1 | 1 | 1 |  |  |  |  |

| r    | 0                  | 1 | 1 | 1 | 0 | 0 | 1 | 0 |  |  |  |  |

| 1    | 0                  | 1 | 1 | 0 | 1 | 1 | 0 | 0 |  |  |  |  |

| d    | 0                  | 1 | 1 | 0 | 0 | 1 | 0 | 0 |  |  |  |  |

**Wavelet Tree.** For wavelet trees, with a parent node at index x the children indexes are 2x + 1 or 2x. Additionally, the cell at level i for character c can be calculated by obtaining the first j bits of the character c, these bits are then the index within the level. The resulting tree structure can be seen in Figure 1.3.

For building the wavelet tree, the first bit of each character is going to get copied into cell 0 at level 0. The second bit is added to the cell 0 of level 1, if the first bit is 0, or cell 1 if the first bit is 1. Recursively this means, that characters in level i from cell x are copied into cell 2x + 1 at level i + 1 if the bit at position x of the character is 1, to cell 2x if the bit at the position is 0.

In Figure 1.3, the example wavelet tree of the input sequence "hello world" is shown.

**Wavelet Matrix.** In the following explanations, a function reverse(b:byte, k:int):byte is required. It takes the first k bits of the byte b and reverses their order, all bits  $\leq k$  are not changed. This means, conceptionally:  $reverse(abcdefgh_b, 4) = dcbaefgh_b$ , and with

concrete numbers:  $reverse(01110000_b, 4) = 11100000_b$ . For each node at index x at level i the children are  $reverse(x, i) \gg 1$  and  $(reverse(x, i) \gg 1) \mid (1 \ll 7)$ . With  $\gg$  and  $\ll$  symbolizing shifting operations. Building the wavelet matrix is the same as building the tree, just with the different formula for calculating the children. The difference in the built structure can be observed in the Figure 1.2 When constructing the wavelet matrix, the first child is used for insertion if the bit at position i is 0, the second child is used if the bit is 1. Additionally, the cell for character c in level i can be calculated by reverse(c, i). Building the wavelet matrix is the same as the tree above. However, the children have a different positioning, as it can be seen in Figure 1.4 compared to Figure 1.3. This repositioning of the children has the advantage, that this lowers the amount of complexity required for building the wavelet matrix. This is further explained in the later chapter 2.2.2.

Figure 1.1.: Visualization of a wavelet tree for  $\log \sigma = 4$ . Each cell has always 2 children, and characters initially in the cell, must end up in one of its children. Additionally, the length of all cells of a level is always n.

Figure 1.2.: Visualization of a wavelet matrix for  $\sigma = 4$ . Each cell has always 2 children, and characters initially in the cell, must end up in one of its children. The big difference to the tree is here, that the order of children cells is different.

**Storage of Wavelet Tree and Matrix.** Kaneta [9] is describing a few different ways of storing wavelet structures in memory. The easiest way of storing the wavelet structure is to have one memory object per cell, and each cell has two children cells, which are stored by pointer. The object itself then additionally has a vector of bits stored. This way of storing does not leverage the fact that the length of each line, hence the amount of bits per line, is known. However, when allocating cell per cell, the exact length is not known in the beginning, additionally, the vector of bits might have an overhead, as the smallest addressable entity is a 8 bit word, so there is a worst-case overhead of 7 bits per cell. Following the idea of knowing the bit length per line, a single memory object for storing all bits of the entire structure arises. This object must be  $n \log(\sigma)$  bit long. The bits of all cells of a level are forming the bits of a single line. The memory object can then be allocated as an array of 64 bit words. Figures 1.3 and 1.4 are showing how these layouts look like in memory.

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 |

| 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 0 |

| 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 1 |

| 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 1 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 |

Figure 1.3.: The wavelet tree of the word *hello* world. The vertical lines are showing where each cell starts or ends. Not each line fills all available cells, hence the number of visible cells is not always the maximum that is possible.

Figure 1.4.: The wavelet matrix of the word *hello world*. The vertical lines are separating the 0s cells from the 1s cells. If one cell is empty, no vertical line is added.

#### 1.2.1. Rank / Select Queries on Wavelet Trees and Matrices

Three main queries that are performed on wavelet structures are access, rank, and select queries.

access(pos: int): char: is returning the character on the position pos. For that, the wavelet structure is scanned through from the first level to the last. For each line iterated, a position and cell index is maintained. At level 0, the cell 0 is used, and position initially passed is used. In the iteration, cell and position is adjusted according to the bit retrieved at the position. If the bit is 1, the right child cell is taken, and the position is updated to the number of 0's + the number of 1's until the position. If the bit is 0, the left child cell is taken, the the position is updated to the number of 0's. In each iteration the retrieved bit is captured. The concatenation of these bits is the results from the access query.

rank(a:char,pos:int):int: is returning the number of character a that is occurring until pos. For that, like in access, a cell index and position is maintained. At the first iteration position is what got passed, and cell is 0. In each iteration the the bit from that level is taken out of a, if the bit is 1, the right child cell is selected, and position is set the number of 0's + the number of 1's until the current position. After the iterations the starting bit of the cell is retrieved. The result of the function is then  $position-cell_{starting}$ .

select(a:char, x:int):int: is returning the position of the n'th occurrence of a. For this, a stack of  $min_i$  and  $max_i$  per level i is maintained. Initially for level 0  $min_0 = 0$  and  $max_0 = n$ . Then, in every line,  $min_{i+1}$  and  $max_{i+1}$  are set according to the ith bit in a. If this bit is 1, then  $min_{i+1} = min_i + count_0(min_i, max_i)$  If this bit is 0, then  $max_{i+1} = max_i - count_1(min_i, max_i)$  When this algorithm has reached the last level, then  $cell_{min}$  and

$cell_{max}$  are the boundaries of the cell that is addressed by a. For the lowest level  $min_{\log \sigma} + x$  is the position in the bit vector, that is describing the x'th occurrence of a in the string. Now, this position needs to be maintained up to level 0 in order to get the real position. For that, the iteration starts at the lowest level with p = x. For each level at i, the position for i - 1 can be calculated. If  $min_i = min_{i-1}$  and  $max_i = max_{i-1}$ , then the position is not updated. If  $min_i = min_{i-1}$  and  $max_i \neq max_{i-1}$ , then the bit at level i - 1 was 0, and the new position is the pth zero between  $min_{i-1}$  and  $max_{i-1}$ . If  $min_i \neq min_{i-1}$  and  $max_i = max_{i-1}$ , then the bit at level i - 1 was 0, and the new position is the pth one between  $min_{i-1}$  and  $max_{i-1}$ . Finally, the the position is stored again into p. When this is executed until i - 1 = 0, then the position in the input string is found.

#### 1.3. Additional Instructions

For exploiting word parallelism, Kaneta is using instructions like *pext* and *pshufl*. In this work, only the *pext* versions are implemented. Additionally *popcnt* is used for queries. The *pext* instruction is part of the *BMI2* (Bit Manipulation Instruction Set 2) instruction extension. It was first introduced in Haswell processors of Intel and the Excavator architecture from AMD.

The instruction *popent* is from the *ABM* (Adcanced Bit Manipulation) according to AMD, Intel considers it as part of SSE4.2.

**pext Instruction.** The *pext* instruction can be explained as pext(a:word, mask:word): word where word can be a 8/16/32/64 bit word. The bits of the result are extracted from a, where the mask bits are 1. Those extracted bits are then shifted to the right. The semantics of the instruction can also be explained with the Figure 1.5. In the following work,  $\beta$  is used to express the amount of bits processed as once with a single *pext* instruction.

**popcnt Instruction.** The *popcnt* instruction is counting the set bits in a passed word. The passed word can be a 8/16/32/64 bit word.

Figure 1.5.: Explanation of the pext semantics. A/B/C/D/E/F/G/H are placeholders for bits.

## 1.4. Algorithem Parallelization

The algorithms in this work are implemented using C++. C++ has several threading frameworks. For example: boost, posix-threads, OpenMP. As this work is closely following PWM, the same framework, OpenMP, is used in this work. This framework allows to execute for loops and entire blocks in parallel. Additionally, the framework provides barriers for synchronization.

In general, parallelization can happen in two ways, either by splitting the problem into

parts, where each part gets solved in parallel, and then merged back into a single solution. Or by an individual algorithm, which does not use any sequential algorithm.

**Domain Decomposition.** The definition of domain decomposition, outside the scope of wavelet trees, from [3] is "Domain decomposition refers to partitioning of computational work among multiple processors by distributing the computational domain of a problem, in other words, data associated with the problem". This explains in a general way, that a sequential algorithm can be parallelized, under the assertion that multiple solutions can be merged into a single one. For implementing a solution like this, first the input is divided into multiple parts, which are solvable on their own. Then every part is computed with the sequential version of the algorithm. Finally, the solution of each computation must be merged into a single solution. The merging itself can then be parallelized again. However, not every problem can be split up into useful parts. As an example, calculating prefix sums can be split into different sub arrays. However, the merging back together part will take as much time as normally calculating the entire prefix sum, which renders the parallelization useless. However, a problem like creating a histogram over an int array is perfectly capable of being solved by domain decomposition, each thread can walk a part distinguished part of the input, the histogram of each thread can then be simply merged together by adding every cell of the histogram into the final one.

In the Section 3.1 this principle is applied to the problem of wavelet tree construction. The exact principal for merging solutions will be explained there.

Individual Parallelization. An alternative idea to domain decomposition is to run smaller parts of the algorithm in parallel. For that, different sequential operations can be broken up into different threads, just like in domain decomposition. The improvement here over the domain decomposition is, that by choosing the place for parallelization the time spend in merging the results can be minimized. To follow the example of histogram building, each thread could be assigned a range of elements where only that single thread is building the histogram for. This would result in the fact that no merging would be required. As each cell of the final histogram would only be written by a single thread. However each thread would have to scan the entire input.

**Runtime Analysis of Parallel Algorithms.** In order to analyze parallel algorithms the *work-time* (also called *work-depth*) model described in [6] as well as [11] is used. In this model the algorithm is analyzed by its *work* and by its *depth*. The analyzed work W is expressing how many operations are required in order to fully execute the algorithm. The depth D is expressing how long the longest single execution path from the beginning to the end is. The variable p is used to express the number of available parallel executing units.

Using the construction of the wavelet tree as an example. The input is split into two parts. Now the work W contains the amount of work required to construct the wavelet tree for the one half, as well as the other half, and finally the work of merging the solutions back together. The depth D is only the amount of work of one half, and the work required to merge.

After those two values have been analyzed, the parallelism of an algorithm can be expressed by W/D. Using Brent's scheduling theorem from [1], the running time can be bound by W/p + D.

#### 1.5. Contribution

In this work, sequential and parallel wavelet construction algorithms leveraging pext instructions are implemented. These algorithms do have the runtime  $O\left(n\log(\sigma)(\frac{1}{\tau}+\frac{\tau}{\beta})\right)$ . Using *pext* instruction enables extracting a subset of bits out of a  $\beta$  bit long word. The basic idea of this paradigm was introduced by Munro et al. [4] and Babenko et al. [10]. Kaneta implemented these ideas for sequential algorithms and compared them to PWM in [9]. In this work, additionally parallel construction algorithms are performed and compared to PWM. For parallel construction, domain decomposition and parallelization according to Shun [8] are implemented and compared. It was learned, that the Shuns parallelization is too fine granular and therefore caused a too big overhead. More details for that are in Section 4.3. In the evaluation chapter, it is shown that the here implemented algorithms are faster than those in PWM, with the sequential versions for  $\log \sigma > 3$ , with parallel versions for  $\sigma > 7$ . The experiments compare the runtime as well as the memory consumption. While the runtime was able to be lower, the memory required increased. This is a result of the fact, that we need to bring the input into a memory layout where *pext* instructions can be used. The result from these experiments have been, that depending on  $\log \sigma$  and *n pext* algorithms can be faster than PWM. Finally, in Section 4.2 it is evaluated which parameters result in the best runtime.

## 2. Sequential Algorithms

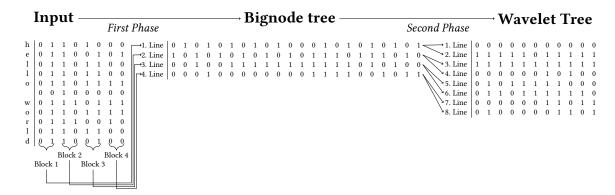

The construction algorithm described here follows the same pattern the algorithms from Munro et al. [4] and Babenko et al. [10] are following. They are splitting the construction into two phases, in the first, the *bignode tree* is constructed. In the second, the bignode tree is used to fill the final result. This second phase utilizes *pext* instructions, this leverages parallel processing of  $\beta$  bit long words. In Figure 2.1 this concept of the two phases is visualized. In this work here, this parallel processing of multiple bits is done with the so called *pext* instruction. Munro et al. and Babenko et al. are using look up tables for that. The first phase is then only there to create a memory layout that allows this instruction / table lookup to be used.

An addition to the paradigm from Munro et al. and Babenko et al. is the construction of a histogram in the first phase of the algorithm. This strategy is also used by Dinklage et al. [2] in the construction algorithms of PWM. Further more, this chapter explains two different ways to implement the wavelet tree. Over the process of this chapter, it is assumed, that  $\tau < \log \sigma < n$ .

#### **Wavelet Structure Construction using two Phases**

Figure 2.1.: Overview showing the relation between input, first phase, second phase, bignode tree, and resulting wavelet tree. The arrows of the first phase display that these values are represented in the associated line. The arrows of the second phase show in which lines the *pack* operation results are stored.

### 2.1. Bignode Tree Building

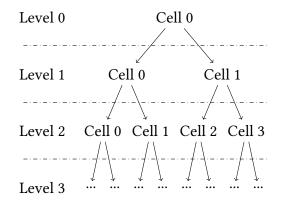

The bignode tree is a tree like structure. Each node of the tree has  $2^{\tau}$  children. Each child edge is associated with an  $id \in [0, 2^{\tau} - 1)$ . In this work, the level of the node, is the level

of the parent plus one. This results in  $i \in [0, \left\lceil \frac{\log \sigma}{\tau} \right\rceil)$ . The root node has the level 0. Each level has  $2^{i \cdot \tau}$  nodes. Every node consists of  $\tau$  bit long blocks. The sum of all blocks per node in level i is n. The node of a level i has an index x which is the bit wise concatenation of all edge ids, starting at root, going to the current node.

In order to get  $\tau$  bit long blocks from the input character, the characters bit representation is split after  $\tau$  bits. Which results in each character having  $\left\lceil \frac{\log(\sigma)}{\tau} \right\rceil$  blocks. As an example, the bit representation of 'h' is  $h := 01101000_b$  with  $\log \sigma = 8$ , its block representation is looking like:

$$h = 01 \quad 10 \quad 10 \quad 00$$

In case there are not enough bits in the original character, the missing ones are filled up with zeros.

**Histogram.** Before building the bignode tree, a histogram over the input is created. For the histogram, an additional binary tree like structure, which consists out of nodes is built. As its a binary tree, each level i has  $2^i$  nodes, with  $i \in [0, \lceil \log(\sigma) \rceil)$  levels. Each node at level i with position x is storing a counter. The node is counting how many characters are within  $\left[\frac{\sigma}{i_{inverse}}x;\frac{\sigma}{i_{inverse}}(x+1)\right]$  with  $i_{inverse}:=\log(\sigma)-i$ . When later building the bignode tree, only blocks of  $\tau$  bits are stored, therefore the histogram is here storing the number of characters, multiplied with  $\tau$ . Lastly, for each level i the prefix sum over each node at level i is calculated and stored.

The algorithms is build in 3 stages. First, the entire input is walked and the node in level  $\lceil \log \sigma \rceil$  representing the character is increased. Due to the fact that this is a binary tree, the level at  $\lceil \log \sigma \rceil$  has  $\geq \sigma$  nodes. Therefore, each node is addressed by using the number representation of the character. After that, in the second stage, each node in level  $i < \log \sigma$  must be build. Assuming level i+1 is already built, level i is built by calculating the counter of each node x by calculating the sum of both children. The indexes of the two children can be calculated with the formulas from the tree paragraph and matrix paragraph in the section 1.2. As the level at  $\lceil \log \sigma \rceil$  is already filled from the first stage, the histogram is build by walking from the deepest level to the root at level 0. Finally, in the last stage the prefix sum of each node in a level is calculated, by walking over each node of a level and add the previous node to it. The first element of the prefix sum is always 0. This is required in practice as this histogram is used to store the state for bignode building.

After these stages, every last node in a level must be equal to n. For creating the histogram, the entire input must be scanned, which is O(n), for building the histogram,  $O(2^{\lceil \log \sigma \rceil})$  sums must be calculated and assigned. For the prefix sum, each node of the tree must be iterated, which is again in  $O(\log \sigma)$ . This creates the final runtime of:

$$O(n+\sigma) \tag{2.1}$$

Memory wise, only the counters must be stored, which requires words:

$$O(\sigma)$$

(2.2)

**Bignode Tree building.** Finally, the bignode tree is build. In the work of Babenko et al. [10] and Munro et al. [4], this step is described as the first phase. The bignode tree is build as an array of bit vectors. The array is  $\left\lceil \frac{\log \sigma}{\tau} \right\rceil$  long. Each bit vector is  $n\tau$  bits long. These bit vectors are filled by iterating over each character. As already described, a character can be split into blocks. A character is inserted by scanning over each block. For each block, the concatenation of the previous  $\tau$  long blocks is used as an index x to find the correct histogram node at level i. For the first block, the index is 0. When building for a matrix instead of a tree, the index is bit wise reversed. The block is then written into the bit vector i of the bignode tree at the position stored in the histogram cell. The histogram cell is then incremented by  $\tau$ . The result of such a bignode tree is displayed in Figure 2.2. This method is quite similar to the algorithm called *prefix counting* (pc) in [2]. The algorithm is briefly explained in Section 4.4.0.1. However, here always a block consisting of bits is inserted, not just a single bit. Lastly, the bignode tree is a compact memory structure, which is prepared in order to be able to use pext instructions later on.

| 1. Line | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 |

|---------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 2. Line | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 0 | 1 | 0 |

| 3. Line | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 1 | 0 | 1 | 0 | 0 |

| 4. Line | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 0 | 1 | 1 |

Figure 2.2.: Example bignode tree for in the input sequence *hello world* and  $\tau = 2$ .

**Runtime.** In order to create a bignode tree, the entire input is scanned. For every character,  $\left\lceil \frac{\log(\sigma)}{\tau} \right\rceil$  insertions are performed. This results in a runtime of:

$$O\left(n\left\lceil\frac{\log(\sigma)}{\tau}\right\rceil\right) \tag{2.3}$$

This runtime is equal to the first phase described by Babenko et al. [10].

**Memory.** The bignode tree stores  $\lceil \log \sigma \rceil / \tau$  lines of  $\tau \cdot n$  bits. Which results in a requirement of bits of:

$$O(\lceil \log(\sigma) \rceil n) \tag{2.4}$$

This is the same as the wavelet structure itself. In the following section, the bignode tree is used to create the wavelet tree and wavelet matrix.

## 2.2. Creating Wavelet Tree and Wavelet Matrix out of Bignode Tree

For the second phase, the bignode tree is used as an input. On each 64-bit word, the two operations *split & sort* and *pack* can be performed. First, we describe the two operations. Later, we describe how these operations are used to build trees and matrices. In this thesis,

we use  $\beta$  as an abstraction for 64-bit words.

For the two operations, there are two constants,  $\ell$  and h, both are  $\beta$  bits long words. The constant  $\ell$  is the concatenation of blocks where the lowest bit per block is set. The constant h is the concatenation of blocks where the highest bit per block is set. If  $\beta > 0 \mod \tau$ , then the last block is considered incomplete and gets ignored. All blocks are aligned at the MSB. Figure 2.3 is showing the value of  $\ell$  and h for  $\tau = 4$  and  $\beta = 16$ . Bitwise operations for left shifting, right shifting, exclusive or, and are denoted as  $\ll$ ,  $\gg$ ,  $\oplus$ , &. The next two paragraphs will explain two operations that are used over the process of constructing the matrix

| constants |   | blo | ck 0 |   |   | blo | ck 1 |   |   | blo | ck 2 |   | block 3 |   |   |   |  |

|-----------|---|-----|------|---|---|-----|------|---|---|-----|------|---|---------|---|---|---|--|

| $\ell$    | 0 | 0   | 0    | 1 | 0 | 0   | 0    | 1 | 0 | 0   | 0    | 1 | 0       | 0 | 0 | 1 |  |

| h         | 1 | 0   | 0    | 0 | 1 | 0   | 0    | 0 | 1 | 0   | 0    | 0 | 1       | 0 | 0 | 0 |  |

Figure 2.3.: Constant values  $\ell$  and h for  $\tau = 4$ , which are used for *split&sort* and *pack* operations.

**Split & Sort.** The operation is annotated as  $splitsort(block\_position : int, value : word) : (word, word). With the operation, a single <math>\beta$  bit word is virtually split into its blocks. These blocks are then sorted based on the bit at position  $block\_position$ . All blocks with a 0 at  $block\_position$  are inserted into the first word. All blocks with a 1 at  $block\_position$  are inserted into the second word. The first word of the result is called  $L_0$ , the second  $L_1$ , both are also named  $L_x$  with  $x \in \{0, 1\}$ .

In order to calculate that result, first the so called  $check_1$ ,  $check_0$  values are calculated, they are also expressed as  $check_x$  with  $x \in \{0, 1\}$ . After that  $fill_0$  and  $fill_1$  are calculated, they are as well expressed as  $fill_x$  with  $x \in \{0, 1\}$ . Both are  $\beta$  bit long words.  $fill_x$  is getting used as a mask for two pext calls, the result of this called is then the result of the entire call to this operation. The pext instruction has been explained in the introduction at Section 1.3.

The value  $check_x$  consists of blocks, where the lowest bit of a block is 1, if the bit at  $block\_position$  is set to x, 0 otherwise. This can be calculated by:

$$check_1 := (value \gg block\_position) \& \ell$$

(2.5)

And the opposite by:

$$check_0 := check_1 \oplus \ell \tag{2.6}$$

These two formulas do not change the order to the blocks yet. The values do have the relation, that  $\ell = check_1 \& check_0$ . This means, that each block from the *value* is having its lowest bit set in either  $check_1$  or  $check_0$ . So no block is going to be list by calculating a mask out of these two values.

In order to get a mask to select the correct blocks via *pext*, we need to set each bit in a block where the lowest bit is set. This can be calculated by:

$$fill_x := (h - check_x) \oplus h$$

(2.7)

This formula can be explained by looking at the binary representation of a subtraction of a single block. There are two possible ways for the subtraction either the lowest bit in the block is set as in Figure 2.5 or not, as in Figure 2.2. The result performed on an

Figure 2.4.: Subtraction result of a block with a MSB not being set

Figure 2.5.: Subtraction result of a block with a MSB being set

entire 64-bit word is resulting in the concatenation of these results. This can be proven by implicitly splitting the 64-bit word into numerical pieces, where each piece is one block. First, split  $check_x$  into numerical blocks, where each block is  $X_n \in \{0000_b, 0001_b\} = \{0, 1\}$ :

$$check_{x} = \sum_{n=0}^{64/\tau} X_{n} 2^{n\tau}$$

Additionally, the same sum can be build for h:

$$h = \sum_{n=0}^{64/\tau} 2^{\tau - 1} 2^{n\tau}$$

The subtraction  $fill_x = h - check_x$  can now be rewritten as:

$$fill_x = \sum_{n=0}^{64/\tau} (2^{\tau - 1} - X_n) 2^{n\tau}$$

$2^{\tau-1}$  is exactly the value of a in the examples. And  $X_n$  is exactly both possible cases of b. Lastly, the two subtractions do not cause any carryovers for the next block. Hence,  $fill_x$  is just the bit concatenation of the blocks shown in Figure 2.2 and Figure 2.5.

As seen in the example figures, the entire block is set correctly, only the MSB is inverted. This can be repaired by performing xor with the constant h.

For both values of  $fill_0$  and  $fill_1$ , no block positions have been changed yet. The two values do have the relation  $\neg(fill_0 \oplus fill_1) = 0$ . This shows, that for all blocks of the original value, no block is in two masks. Additionally, every block of the original value is going to be masked by one  $fill_x$ . Finally, the here calculated masks are used in two pext calls, which results in the  $L_0$  and  $L_1$ . In order to receive how many blocks in each  $L_x$ , the bits of each mask  $fill_x$  are counted, and divided by  $\tau$ . This procedure can be executed by using the popcnt instructions. However, for the sake of readability, the number of valid blocks per word is not added to the function notation. As an example, Figure 2.6 shows the result and calculated variables of a split&sort call.

**Pack.** This work makes heavy use of bit blocks, that are concatenated into  $\beta$  bit long words. With the *pack* operation, a single bits out of every block is extracted. The extract

| input                        | 0 | 1 | 1 | 0 | 1 | 1 | 0 | 0 |         |       |   |   |   |   |   |   |   |   |

|------------------------------|---|---|---|---|---|---|---|---|---------|-------|---|---|---|---|---|---|---|---|

| $\overline{check_0}$         | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | _       | т     | Λ | 1 | Λ | Λ | l |   | ı |   |

| $check_0$ $check_1$ $fill_0$ | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | Result: | $L_0$ | 1 | 1 | 1 | 1 | _ | _ | _ | - |

| $fill_0$                     | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 1 |         | $L_1$ | 1 | U | 1 | 1 | - | _ | - | - |

| $fill_1$                     | 0 | 0 | 1 | 1 | 1 | 1 | 0 | 0 |         |       |   |   |   |   |   |   |   |   |

Figure 2.6.: Results of the splitsort(0, input) call.  $L_0$  contains all blocks that have a 0 at block position 0.  $L_1$  contains all blocks that have a 1 at block position 1. Each result has two blocks of result.

bits are then written next to each other in a single  $\beta$  long word. The function is called  $pack(block\_position:int,value:word):word.block\_position$  is describing to position of the bit within the block that is going to be extracted. value is the  $\beta$  bit long word, which is the concatenation of bits. This is again done by first calculating a mask, calling pext with this mask, and returning the result. The mask is created, by left shifting the constant  $\ell$  by  $block\_position$ . The formula for that is:

$$mask := \ell \ll block\_position$$

(2.8)

Lastly, the result of the function is simply the *pext* call with the calculated mask. In Figure 2.7 an example call, with the calculated mask is shown.

Result: 0 1 1 0

Figure 2.7.: Results of a pack(1, input) call.

#### 2.2.1. Wavelet Tree Construction

For creating the wavelet tree, the histogram and the bignode tree are passed as input. The goal of building the a wavelet tree is to fill  $\log \sigma$  lines of n bits. This filled structure is then used later in query implementations for answering rank/select/access calls. The way how the wavelet tree is stored, is explained in the introduction at Section 1.2.

Briefly describing what needs to be done in order to construct the wavelet tree: With the bignode tree, a partially sorted tree is given as input. Each bignode tree level i is having the correct sorted order for line  $i \cdot \tau$  in the result, this order only must be extracted into the result using pack operations. All lines in the result at  $i \cdot \tau + \alpha$  with  $0 < \alpha < \tau$  are not in the correct state yet. In order to correct this line, each block in this line must be sorted according to cells in the current line. This can be done, while assuming split&sort operations on a cell cover all blocks of a cell, by calling this operation on every cell of the line i. Every cell is then split into two child cells. These cells are then written next to each other, the exact order how children in a tree are ordered can be seen in Figure 1.1. Finally,

Bignode line:

$$\underbrace{0\quad 0\quad 1\quad 1}_{\text{cell 0}}$$

$\underbrace{0\quad 1\quad 0\quad 0\quad 1}_{\text{cell 2}}$   $\underbrace{0\quad 1\quad 0\quad 0\quad 0\quad 0}_{\text{cell 3}}$

Figure 2.8.: An example histogram line, and bignode line at i=2. The bignode tree line is stored using  $\beta=8$ . There are 4 cells in total, which are stored in 2 8-bit long words.

pack operations are used to extract the correctly sorted blocks.

In order to implement the creation, two additional lines with the sizes of bignode lines are allocated. In the following explanation, we make use of bignode lines associated with a level, written as j. For  $j \equiv 0 \mod \tau$ , j is the  $j/\tau$  line of the originally passed bignode tree. For  $j \not\equiv 0 \mod \tau$ , every j has one of the two additional bignode lines assigned. This assignment ensures, that  $j \neq (j+1)$ . To build the tree, each level  $i \in [0, \lceil \log \sigma \rceil)$ is iterated. In every level i, each  $\beta$  long word of the i bignode line is processed with the pack operation, and the results are written into the ith line of the result buffer. If  $i \not\equiv \tau - 1$ mod  $\tau$ , all cells  $x \in [0, 2^l)$  are iterated. The exact starting position of each cell can be received from the histogram. For every  $\beta$  bit long word, that contains blocks from the cell *x*, *split&sort* must be executed. This exact task can be implemented in two different approaches, either by iterating cell by cell, or word by word. In the following paragraphs two implementations are explained, that are used to perform split&sort operations on all cells of a single line in the bignode tree. In order to explain the results better, we denote the results  $L_0$  and  $L_1$  of a single *split&sort* operation on a cell x, described as  $r_{x,0} = L_0$  and  $r_{x,1} = L_1$ . The result of both implementations is a bignode tree line with the content of:  $r_{0,0} \cdot r_{0,1} \cdot r_{1,0} \cdot r_{1,1} \cdot r_{i,0} \cdot r_{i,1} \dots$ , where  $\cdot$  is interpreted as bit wise concatenation.

#### 2.2.1.1. Using Cell Iteration.

Implementing this can be done by iterating over each cell x and its boundaries. This explanation will call i the index of the current line. The boundaries [z,y) can be fetched from the histogram. From these boundaries the first, and last id of  $\beta$  bit long word can be calculated by  $id_{first} = z/\beta$  and  $id_{last} = y/\beta$ . These words can then be iterated, and the split&sort operation on a single,  $\beta$  bit long word can be performed. Each  $L_0$  and each  $L_1$  can then be stored in the buffer of the next line. The position where to store  $L_0$  or  $L_1$  can be received from the histogram. To receive the exact position, the line i and cell x \* 2 and cell x \* 2 + 1 can be read. After  $L_0$  and  $L_1$  is written, the histogram cells containing the positions are updated accordingly. If a  $\beta$  bit long word is not entirely within a cell, a mask is used to mask the  $fill_x$  variables in the split&sort operation, to only contain the blocks that are part of the cell.

As an example, Figure 2.8 is showing a line at i=2 in the bignode tree, storing blocks within a  $\beta=8$ . As it is in i=2, there are 4 cells. Cell 0 is 2 blocks long, cell 1 is 1 block long, cell 2 is 2 blocks long, and cell 3 is 6 blocks long. The two words, which are used to

store the blocks are called w0 and w1. In order to process this line using the cell iterator, these 5 *split&sort* calls are done: w0 for cell 0, w0 for cell 1, w0 for cell 2, w1 for cell 2, w1 for cell 3. All of them have a mask applied in order to only process the blocks of the correct cell.

#### 2.2.1.2. Using Word Iterator.

As shown in the previous paragraph, using the cell iterator results in multiple calls to split&sort with the same word. By iterating over each word, performing split&sort on it, and splitting  $L_0$  and  $L_1$  after each call. The split results are then stored in the i+1 bignode tree line. When inserting  $L_0$ , we know that this is going to be in the position denoted as  $x_0$ , insertions of  $L_1$  will go into position  $x_1$ . The splitting can be done, by checking how many blocks still need to be added to a cell, using the histogram. As explained in Paragraph histogram of Section 2.1, the cells of the histogram are a prefix sum, so the size of a cell in the wavelet tree can be calculated by subtracting the prefix sum at position x minus the position at x-1. When the processing of the line starts,  $x_0$  is zero and  $x_1$  is one. When processing a word, the result  $L_0$  is stored at the bit position in the histogram at  $x_0$ . When it is detected that the number of blocks in  $L_0$  is bigger than the space left in the cell  $x_0$ , then  $x_0$  is increased by 2, and the remaining blocks are stored in the new cell. If this cell is also not having enough space, the process of increasing  $x_0$  and storing the next blocks there is repeated. The same process is repeated for storing the blocks of  $L_1$ . After each write of blocks, the histogram is updated accordingly.

Simulating this approach again for the example bignode line from Figure 2.8 will now only call *split&sort* two times, once for w0 and once for w1. However, comparing it to the cell iterator shows, that there is a logic overhead for handling the splits

#### 2.2.2. Wavelet Matrix Construction

As described in Section 1.2, the difference between wavelet matrix and wavelet tree is the ordering of cells. The impact of that can be seen best in *split&sort* by rebuilding the word iterator approach for this. In order to reuse the word iterator approach for this, the formulas for calculating the children must be remodeled. In this case,  $x_0$  is initialized with 0,  $x_1$  is initialized with the value in the histogram cell at  $2^{i-1}$ . This value is equal to the amount of zeros in the i'th level. Finally,  $x_0$  and  $x_1$  must be increased by one, if the cell is full. This means, that when the cell is full, the blocks will simply be added to the next word, which is equal to inserting the entire  $L_x$  to where the last write ended. This means, that the defined order of cells, removes the need to split the  $L_x$  results. This can also be seen when looking at the matrix visualization from the introduction in Figure 1.2.

For implementing the matrix creation, the same basic setup as for tree building is taken, the two additional bignode tree lines are allocated, and the same annotation, i, is used in order to express which bignode tree line is read / written to. Now, finally building the matrix, each level  $i \in [0, \lceil \log \sigma \rceil)$  is iterated. In every level i, each  $\beta$  long word of the i bignode line is processed with the pack operation, and the results are written into the ith line of the result buffer. If  $i \not\equiv \tau - 1 \mod \tau$ , each  $\beta$  bit long word of i is iterated and split using split&sort operation. In order to write each  $L_0$  and each  $L_1$  two indexes

are maintained, called  $id_0$  and  $id_1$ .  $id_0$  is initialized with 0, and  $id_1$  with the value of the histogram at level i and cell  $2^{i-1}$ . For each *split&sort* operation, the resulting blocks in  $L_0$  are written to the bit index stored in  $id_0$ . The blocks of  $L_1$  to the bit index stored in  $id_1$ . After these writes,  $id_0$  and  $id_1$  are updated accordingly.

#### **2.2.3.** Influence of $\tau$

As a short recap, the parameter  $\tau$  is defining the number of bits per block in the bignode tree. Every line stores n blocks of bits. They are stored in  $\beta$  bit long words. Later on in the construction, these  $\beta$  bit long words are used for executing pext instructions. These instructions are used to leverage the possibility of parallel sorting using split&sort operations. In practice, the bit vectors are stored as 64-bit words, so  $\left\lfloor \frac{64}{\tau} \right\rfloor$  blocks can be stored per word. Hence, a higher  $\tau$  results in a lower number of blocks in a single  $\beta$  bit long word. Which overall results in a lower amount of parallelism leverages by split&sort operations. However, a higher  $\tau$  also means, that the bignode tree creation does iterate over fewer blocks per character, and fewer memory writes in this phase are performed. Which lowers the expected runtime. This shows that  $\tau$  must be evaluated while executing real runs, as the parameter can be used to move work between the first and second phase of the construction. The whole outcome of this effect is compared in the evaluation chapter 4.

#### 2.2.4. Runtime

For transferring a bignode line to a result line,  $O\left(\left\lceil\frac{n\tau}{\beta}\right\rceil\right)$  *split&sort* operations are required. This is ignoring that in tree creation, using the cell iterator approach, multiple *split&sort* operations are performed for the same word. Finally,  $\log(\sigma)$  lines are getting transferred, therefore the complete transferring takes:

$$O\left(\left\lceil \frac{n\tau}{\beta}\right\rceil \log(\sigma)\right) \tag{2.9}$$